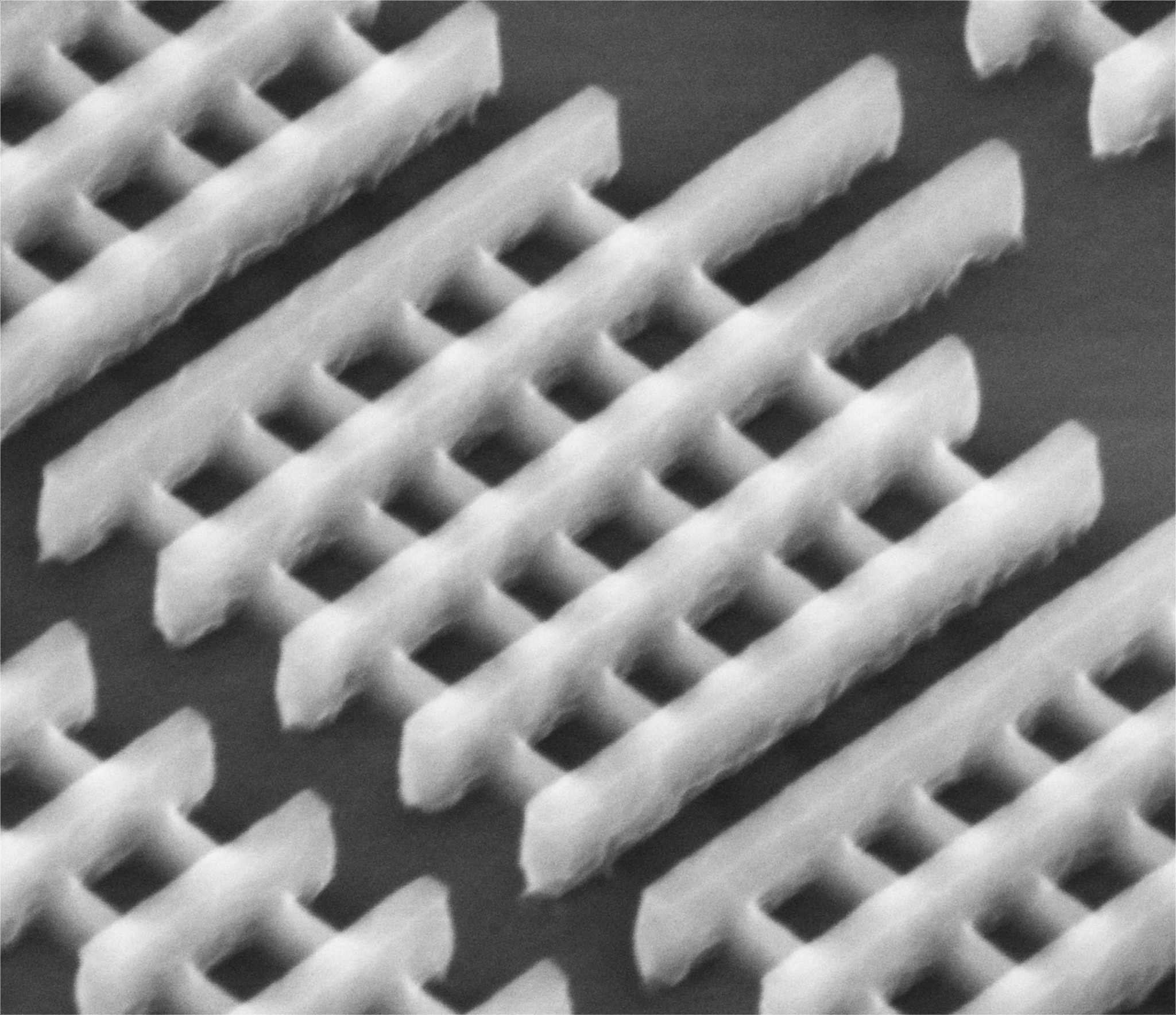

Intel's 3D tri-gate transistors have a feature size of only 22 nm. The thin structures are the silicon channels, the thicker ones are the gates and the contacts. Several gates can be used next to each other to enhance the efficiency of the switching. (c) Intel

Finally I am getting around to blog about the latest generation of transistors that Intel presented earlier this months. These transistors reach feature sizes of only 22 nanometres, down from 32 nm. To give you some perspective what this amazingly high integration means: 4,000 of those 22 nm structures fit across the width of a human hair, or similarly, 100 million of these transistors fit on the head of a pin.

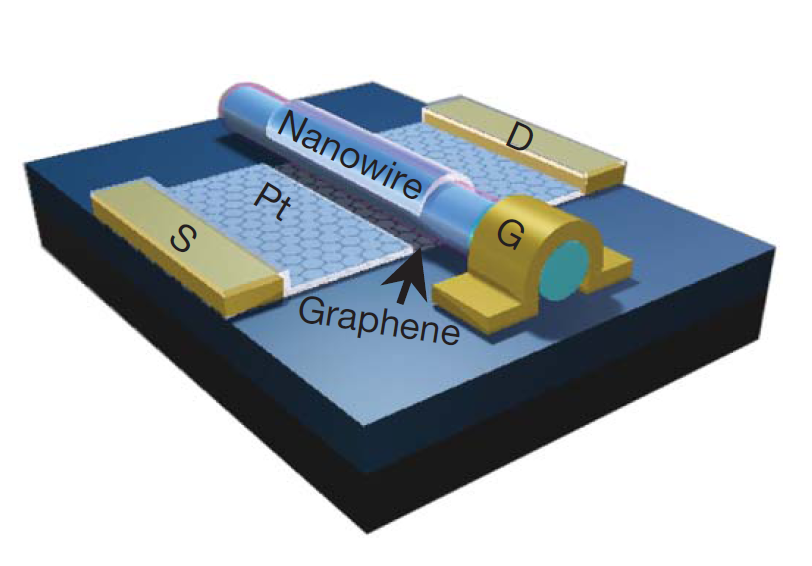

Now how did they reduce transistor length scales down by almost a third? Well, even though Intel (and others) is in the business of shrinking transistor for more than 40 years, this time it’s a bit more than a mere scaling exercise. For the first time we have a commercial 3D transistor design on such a scale. In a typical ‘field-effect’ transistor, two electrical contacts are used to run an electric current through a silicon layer. The transistor is switched between an electrically conducting and an insulating state by a gate on top of the silicon. The voltage applied to that gate determines whether current can flow or not. Thereby the gate is able to set the digital ‘1’ and ‘0’ in a transistor.

A problem in shrinking transistors has been the fact that those three electric contacts need a certain minimum space of their own. Furthermore, as the gate has become smaller and smaller, it has been increasingly inefficient to switch the electric current in the silicon layer underneath. For smaller gates the electric fields from the gate just don’t reach that far down into the silicon layer. […]

May 26, 2011

9 Comments